在計(jì)算機(jī)系統(tǒng)結(jié)構(gòu)的學(xué)習(xí)中,流水線技術(shù)是提升處理器性能的核心設(shè)計(jì)思想之一。它通過將指令執(zhí)行過程分解為多個(gè)階段,并讓多條指令在不同階段重疊執(zhí)行,從而實(shí)現(xiàn)了指令級(jí)并行,顯著提高了處理器的吞吐率。本部分復(fù)習(xí)筆記將系統(tǒng)梳理流水線技術(shù)的關(guān)鍵概念,并探討其與底層電子技術(shù)開發(fā)的緊密互動(dòng)與共同演進(jìn)。

一、流水線技術(shù)的基本原理與性能分析

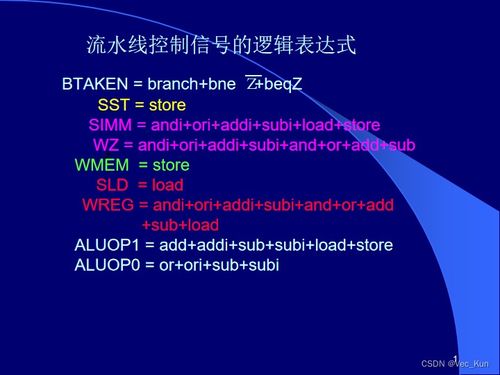

經(jīng)典的5級(jí)RISC流水線(取指IF、譯碼ID、執(zhí)行EX、訪存MEM、寫回WB)是理解流水線的基礎(chǔ)模型。其理想加速比公式為 Speedup = Tnon-pipeline / Tpipeline ≈ N(階段數(shù)),但實(shí)際中由于結(jié)構(gòu)冒險(xiǎn)、數(shù)據(jù)冒險(xiǎn)和控制冒險(xiǎn)的存在,加速比會(huì)低于理想值。

- 冒險(xiǎn)與解決策略:

- 結(jié)構(gòu)冒險(xiǎn):硬件資源沖突。解決方法包括資源重復(fù)(如分離指令和數(shù)據(jù)緩存)和流水線停頓。

- 數(shù)據(jù)冒險(xiǎn):后續(xù)指令需要等待前序指令的數(shù)據(jù)。解決方法包括轉(zhuǎn)發(fā)(旁路)技術(shù)、流水線停頓以及編譯器調(diào)度(靜態(tài)調(diào)度)。

- 控制冒險(xiǎn):分支指令導(dǎo)致的指令流改變。解決方法包括分支預(yù)測(靜態(tài)預(yù)測、動(dòng)態(tài)預(yù)測如兩位飽和計(jì)數(shù)器、分支目標(biāo)緩沖BTB)、延遲槽技術(shù)等。

- 性能度量:吞吐率(單位時(shí)間完成的指令數(shù))和加速比是核心指標(biāo)。流水線深度增加可以提高時(shí)鐘頻率,但也會(huì)增加冒險(xiǎn)開銷和寄存器開銷,存在一個(gè)最優(yōu)深度點(diǎn)。

二、現(xiàn)代流水線技術(shù)的深化:超標(biāo)量與動(dòng)態(tài)調(diào)度

為了進(jìn)一步挖掘指令級(jí)并行,現(xiàn)代處理器超越了基本的線性流水線:

- 超標(biāo)量技術(shù):每個(gè)時(shí)鐘周期發(fā)射多條指令到多條并行工作的流水線中。這需要更復(fù)雜的取指、譯碼和提交邏輯,以及多端口寄存器和緩存。

- 動(dòng)態(tài)調(diào)度(亂序執(zhí)行):以Tomasulo算法及其變種為代表,通過保留站、重排序緩沖(ROB)等硬件結(jié)構(gòu),允許指令在操作數(shù)就緒后立即執(zhí)行,克服了假數(shù)據(jù)依賴(名相關(guān)),極大地提高了硬件利用率。動(dòng)態(tài)調(diào)度與分支預(yù)測、推測執(zhí)行緊密結(jié)合,是現(xiàn)代高性能CPU(如Intel Core、AMD Ryzen系列)的核心。

三、流水線技術(shù)與電子技術(shù)開發(fā)的共生演進(jìn)

流水線設(shè)計(jì)的每一次飛躍,都深深植根于同時(shí)代電子技術(shù)的發(fā)展,并反過來推動(dòng)其進(jìn)步。

- 晶體管微縮與時(shí)鐘頻率提升:在半導(dǎo)體工藝遵循摩爾定律飛速發(fā)展的年代,晶體管尺寸縮小使得單芯片上可以集成更復(fù)雜的流水線控制邏輯(如更強(qiáng)大的分支預(yù)測器、更大的ROB)。更高的晶體管開關(guān)速度直接支撐了更深流水線和更高主頻的設(shè)計(jì),追求更高的指令吞吐率。

- 功耗墻與能效優(yōu)先設(shè)計(jì):當(dāng)工藝進(jìn)入納米尺度后,漏電功耗急劇增加,時(shí)鐘頻率和電壓提升遇到瓶頸(功耗墻)。這迫使流水線設(shè)計(jì)從單純追求高頻深流水線(如Intel NetBurst架構(gòu)的Pentium 4)轉(zhuǎn)向更注重能效的設(shè)計(jì):

- 適度流水線深度:避免過深的流水線帶來的分支誤預(yù)測懲罰和功耗開銷。

- 多核與片上眾核:在單線程ILP挖掘接近極限后,通過并行處理技術(shù)(線程級(jí)并行TLP、數(shù)據(jù)級(jí)并行DLP)來提升整體性能,流水線技術(shù)成為每個(gè)核心的基礎(chǔ)。

- 異構(gòu)計(jì)算與特定流水線:為圖形處理(GPU)、AI計(jì)算(NPU)等特定任務(wù)設(shè)計(jì)高度定制化的流水線(如SIMD、SIMT流水線),實(shí)現(xiàn)極高的能效比。

- 存儲(chǔ)墻與內(nèi)存層次結(jié)構(gòu)優(yōu)化:處理器速度遠(yuǎn)快于主存,訪存延遲成為瓶頸。流水線設(shè)計(jì)必須與緩存層次結(jié)構(gòu)協(xié)同:

- 更智能的預(yù)取器被集成在流水線的訪存階段,預(yù)測并提前加載數(shù)據(jù)。

- 非阻塞緩存設(shè)計(jì)允許流水線在緩存缺失時(shí)繼續(xù)執(zhí)行其他不相關(guān)指令,掩蓋延遲。

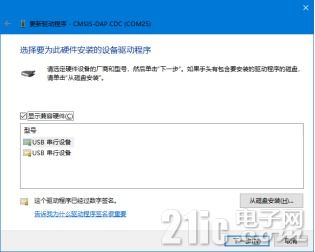

- 這些都需要在芯片上集成更大、更智能的SRAM緩存,這是電子技術(shù)實(shí)現(xiàn)的直接體現(xiàn)。

- 先進(jìn)封裝與系統(tǒng)級(jí)集成:隨著2.5D/3D封裝、Chiplet等電子集成技術(shù)的發(fā)展,可以將不同工藝、不同功能的計(jì)算單元(如CPU核、GPU核、IO單元)集成在一起。這使得系統(tǒng)級(jí)的“流水線”或“處理鏈路”成為可能,例如將數(shù)據(jù)從網(wǎng)絡(luò)接口通過高速互連直接“流水”到處理單元,再“流水”到存儲(chǔ)單元,整個(gè)路徑的優(yōu)化超越了單芯片內(nèi)流水線的范疇。

四、與展望

流水線技術(shù)是計(jì)算機(jī)體系結(jié)構(gòu)中連接軟件指令流與硬件物理實(shí)現(xiàn)的橋梁。從經(jīng)典的線性流水線到復(fù)雜的超標(biāo)量亂序執(zhí)行引擎,其演進(jìn)始終與半導(dǎo)體工藝、電路設(shè)計(jì)、功耗管理和封裝技術(shù)等電子技術(shù)開發(fā)同頻共振。面對(duì)后摩爾時(shí)代,流水線技術(shù)將繼續(xù)與新型器件(如存算一體)、光互連、近內(nèi)存計(jì)算等電子技術(shù)創(chuàng)新結(jié)合,在提升性能、降低能耗、支持新興應(yīng)用(如AI、量子計(jì)算經(jīng)典控制)等方面探索新的形態(tài),持續(xù)推動(dòng)計(jì)算系統(tǒng)向前發(fā)展。

(本筆記旨在提綱挈領(lǐng),具體細(xì)節(jié)如算法實(shí)例、定量分析、具體型號(hào)處理器案例等需結(jié)合教材與課堂內(nèi)容進(jìn)行深化復(fù)習(xí)。)